# GLF4028 High Efficiency Power Mux IC

**Product Specification**

## DESCRIPTION

The GLF4028 is an integrated power multiplexer switch with dual independent power switches connected to a single output pin to enable seamless transition between two input sources.

The GLF4028 provides a manual selection mode by the combination of the logic input pins of EN and SEL. The EN input pin is used along with the select (SEL) input pin to select VIN1 only, select VIN2 only, or turn both switches off.

The GLF4028 features an ultra-efficient  $I_QSmart^{TM}$  technology that offers quiescent current ( $I_Q$ ) and shutdown current ( $I_{SD}$ ) in the industry. Low  $R_{ON}$  reduces conduction losses while low  $I_Q$  and  $I_{SD}$  solutions help designers to reduce parasitic leakage current, improve system efficiency, and increase battery lifetime.

The GLF4028 blocks any cross-conduction current between two input power sources. When the switch is disabled, the GLF4028 prevents the reverse current to the input source from the output at any higher VOUT than VIN condition.

## **FEATURES**

- Two-Input and Single-Output Power Multiplexer Switch

- Supply Voltage Range: 2.5 V to 5.5 V

- R<sub>ON</sub>: 97 mΩ Typ. at 5.5 V<sub>IN1</sub> or V<sub>IN2</sub>

105 mΩ Typ. at 4.5 V<sub>IN1</sub> or V<sub>IN2</sub>

- 2 A Continuous Output Current Capability Per Channel

- Ultra-Low Supply Current at Operation  $I_Q$ : 3 µA Typ at 5.5 V<sub>IN</sub>

- Ultra-Low Stand-by Current

I<sub>SD</sub>: 5 nA Typ at 5.5 V<sub>IN</sub>

- Smart Control Pins

I<sub>EN</sub> and I<sub>SEL</sub> : 3 nA Typ at V<sub>EN</sub> or V<sub>SEL</sub> > V<sub>IH</sub>

R<sub>EN</sub> and R<sub>SEL</sub> : 500 kΩ Typ

- No Cross Conduction Between Two Inputs

- Reverse Current Blocking when Disabled

- Operating Temperature Range: -40 °C to 85 °C

- HBM: 6 kV, CDM: 2 kV

## APPLICATIONS

- Smart Devices

- Smart Home Electronics

## **DEVICE ORDERING INFORMATION**

| Part Number  | Top Mark | $R_{ON}$ at 5.5 $V_{IN}$ | Output Current, IOUT | Ultra-low $I_{\text{Q}}$ at 5.5 $V_{\text{IN}}$ |

|--------------|----------|--------------------------|----------------------|-------------------------------------------------|

| GLF4028-T2G7 | EP       | 97 mΩ                    | 2 A                  | 3 µA                                            |

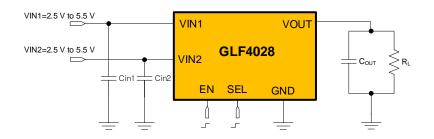

## **APPLICATION DIAGRAM**

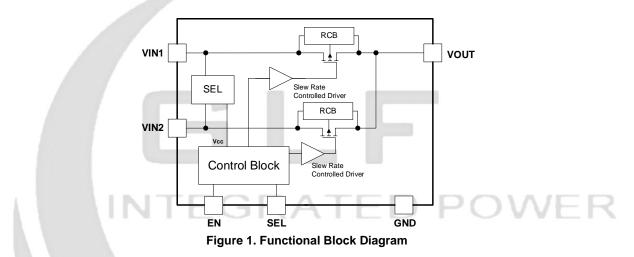

## FUNCTIONAL BLOCK DIAGRAM

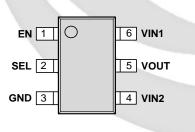

## **PIN CONFIGURATION**

Figure 2. SOT23-6L

## **PIN DEFINITION**

|       | Pin #                                            | Name | Description                                                     |

|-------|--------------------------------------------------|------|-----------------------------------------------------------------|

|       | 1                                                | EN   | Enable to control the switch. Do not leave the EN pin floating. |

| 2 SEL |                                                  | SEL  | Input Source Selection. Do not leave the SEL pin floating.      |

|       | 3      GND        4      VIN2        5      VOUT |      | Ground                                                          |

|       |                                                  |      | Switch Input 2                                                  |

|       |                                                  |      | Switch Output                                                   |

|       | 6                                                | VIN1 | Switch Input 1                                                  |

# **GLF** INTEGRATED POWER

# GLF4028 High Efficiency Power Mux IC

## **ABSOLUTE MAXIMUM RATINGS**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions; extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                 | Pa                                       | arameter                          | Min. | Max. | Unit |

|------------------------|------------------------------------------|-----------------------------------|------|------|------|

| VIN1, VIN2<br>VOUT, EN | Each Pin Voltage Range to GND            | -0.3                              | 6.5  | V    |      |

| Іоит                   | Maximum Continuous Switch Current        |                                   |      | 2.0  | А    |

| Po                     | Power Dissipation at $T_A = 25^{\circ}C$ |                                   | 1.0  | W    |      |

| Tstg                   | Storage Junction Temperature             | -65                               | 150  | °C   |      |

| TA                     | Operating Temperature Range              | -40                               | 85   | °C   |      |

| θ」с                    | Thermal Resistance, Junction to Case     |                                   |      | 90   | °C/W |

| θ <sub>JA</sub>        | Thermal Resistance, Junction to Ambient  |                                   |      | 180  | °C/W |

|                        | Electrostatic Discharge Capability       | Human Body Model, JESD22-A114     | 6    |      | k) / |

| ESD                    | Electrostatic Discharge Capability       | Charged Device Model, JESD22-C101 | 2    |      | kV   |

Notes: 1. The thermal resistance depends on the PCB layout and heat dissipation.

# **RECOMMENDED OPERATING CONDITIONS**

| Symbol     | Parameter                     | Min. | Max. | Unit |

|------------|-------------------------------|------|------|------|

| VIN1, VIN2 | Supply Voltage                | 2.5  | 5.5  | V    |

| TA         | Ambient Operating Temperature | -40  | +85  | °C   |

# GLF4028 High Efficiency Power Mux IC

# **ELECTRICAL CHARACTERISTICS**

$V_{\text{IN1}}$  =  $V_{\text{IN2}}$  = 2.5 V to 5.5 V and  $T_{\text{A}}$  = 25°C. Unless otherwise noted

| Symbol                             | Parameter                        | Conditions                                                                                              |                                                                     | Min. | Тур | Max | Unit |

|------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------|-----|-----|------|

| Basic Oper                         | ation                            |                                                                                                         |                                                                     |      |     |     |      |

| lq1, lq2                           | Quiescent Current                |                                                                                                         |                                                                     |      | 3   | 4.5 | μA   |

|                                    |                                  | As above, $T_A = 85^{\circ}C^{(1)}$                                                                     |                                                                     | 4    |     |     |      |

|                                    |                                  | V <sub>IN1,2</sub> = 5.5 V, V <sub>OUT</sub> = GND, EN = SEL = 0 V                                      |                                                                     |      | 5   | 20  |      |

| ISD1, ISD2                         | Shutdown Current                 | $V_{IN1,2} = 5.5 \text{ V}, V_{OUT} = \text{GND}, \text{ EN} = \text{S}$<br>$T_A = 85 \text{ °C}^{(1)}$ | EL = 0 V,                                                           |      | 50  |     | nA   |

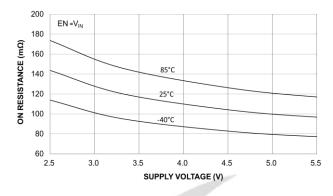

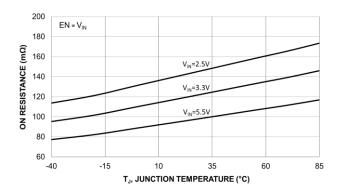

|                                    |                                  |                                                                                                         | T <sub>A</sub> = 25 °C                                              |      | 97  | 107 |      |

|                                    |                                  | $V_{IN1}$ or $V_{IN2}$ = 5.5 V, $I_{OUT}$ = 500 mA                                                      | $T_A = 85 \ ^{\circ}C \ ^{(1)}$                                     |      | 115 |     |      |

| Paul                               | On-Resistance                    |                                                                                                         | $T_{A} = 85 \ ^{\circ}C^{(1)}$                                      |      | 105 | 118 | - mΩ |

| Ron                                | On-Resistance                    | $V_{IN1}$ or $V_{IN2}$ = 4.5 V, $I_{OUT}$ = 500 mA                                                      |                                                                     |      | 125 |     |      |

|                                    |                                  | $V_{IN1} \text{ or } V_{IN2} = 3.3 \text{ V}, I_{OUT} = 300 \text{ mA}$                                 |                                                                     |      | 120 | 135 |      |

|                                    |                                  | $V_{IN1}$ or $V_{IN2}$ = 2.5 V, $I_{OUT}$ = 100 mA                                                      | $I_1 \text{ or } V_{IN2} = 2.5 \text{ V}, I_{OUT} = 100 \text{ mA}$ |      | 145 | 162 |      |

| VIH                                | EN, SEL Input Logic High Voltage |                                                                                                         |                                                                     | 1.2  |     |     | V    |

| VIL                                | EN, SEL Input Logic Low Voltage  |                                                                                                         |                                                                     |      |     | 0.4 | V    |

| I <sub>EN</sub> , I <sub>SEL</sub> | EN, SEL Current                  | $V_{EN} \text{ or } V_{SEL} > V_{IH}, Enabled$                                                          |                                                                     |      | 3   | 20  | nA   |

| REN, RSEL                          | EN, SEL Pulldown Resistance (1)  | $V_{EN}$ or $V_{SEL} < V_{IL}$ , Disabled                                                               | PO                                                                  | S    | 500 | R   | kΩ   |

| IRVS                               | Reverse Current <sup>(1)</sup>   | $V_{IN1} = V_{IN2} = 0 V$ , $V_{OUT} = 5.5 V$ , $EN = S$                                                | EL=0 V                                                              |      | 2.5 |     | μA   |

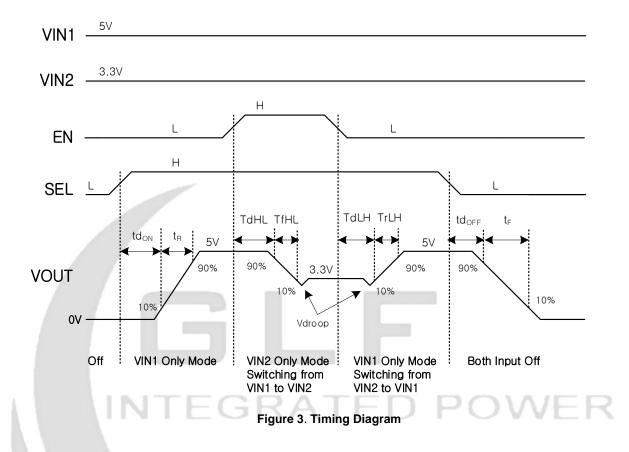

| Switching C                        | Characteristics <sup>(2)</sup>   |                                                                                                         |                                                                     |      |     |     |      |

| t <sub>dON</sub>                   | Turn-On Delay                    |                                                                                                         |                                                                     |      | 250 |     |      |

| t <sub>R</sub>                     | VOUT Rise Time                   |                                                                                                         |                                                                     |      | 340 |     |      |

| TdHL                               | High-low Delay <sup>(1)</sup>    | ]                                                                                                       |                                                                     |      | 3   |     | μs   |

| TfHL                               | High-low Fall Time (1)           |                                                                                                         |                                                                     |      | 6   |     |      |

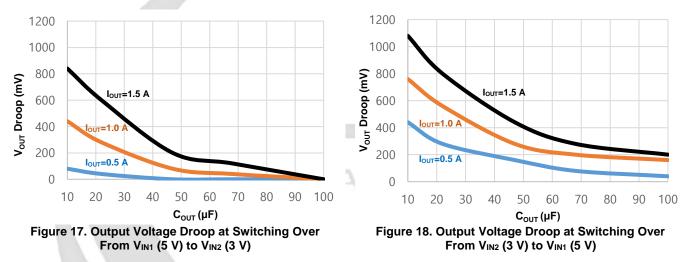

| Vdroop                             | Voltage Droop <sup>(1)</sup>     | V <sub>IN1</sub> = 5 V, V <sub>IN2</sub> = 3.3<br>R <sub>L</sub> =150 Ω, C <sub>OUT</sub> =1.0 μ        |                                                                     |      | 120 |     | mV   |

| TdLH                               | Low-high Delay <sup>(1)</sup>    |                                                                                                         |                                                                     |      | 7   |     |      |

| TrLH                               | Low-high Rise Time (1)           |                                                                                                         |                                                                     |      | 4   |     |      |

| tdoff                              | Turn-Off Delay <sup>(1)</sup>    |                                                                                                         |                                                                     |      | 13  |     | μs   |

| t <sub>F</sub>                     | VOUT Fall Time (1)               |                                                                                                         |                                                                     |      | 350 |     | 1    |

Notes: 1. By design; characterized, not production tested.

2.  $t_{ON} = t_{dON} + t_R$ ,  $t_{OFF} = t_{dOFF} + t_F$

## TIMING DIAGRAM AND TRUTH TABLE

| SEL | EN | Function              | VOUT   |

|-----|----|-----------------------|--------|

| 0   | 0  | Both switches are off | High-Z |

| 1   | 0  | Only VIN1 is selected | VIN1   |

| 1   | 1  | Only VIN2 is selected | VIN2   |

Table 1. Truth Table of Input Source Selection

# TYPICAL PERFORMANCE CHARACTERISTICS

Figure 4. On-Resistance vs. Supply Voltage

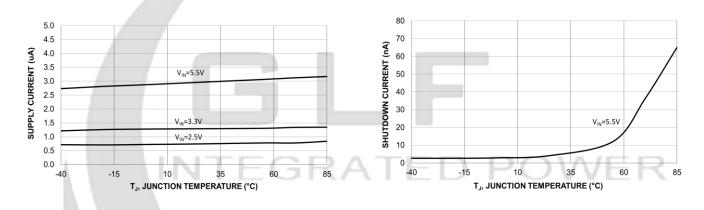

#### Figure 6. Quiescent Current vs. Temperature

Figure 8. EN and SEL Input Logic High Threshold vs. Temperature

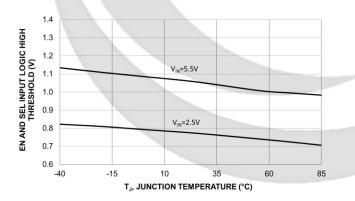

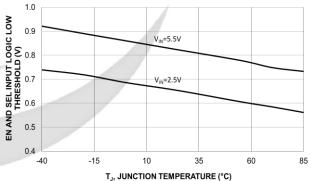

Figure 7. Shutdown Current vs. Temperature

Figure 9. EN and SEL Input Logic Low Threshold vs. Temperature

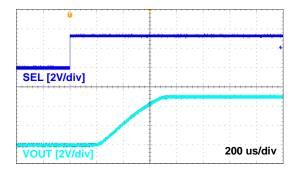

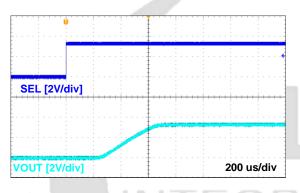

Figure 10. Turn-On Response VIN1=5 V, CIN=0.1  $\mu$ F, COUT=1.0  $\mu$ F, RL=150  $\Omega$

Figure 12. Turn-On Response VIN1=3.3 V, CIN=0.1  $\mu$ F, COUT=1.0  $\mu$ F, RL=150  $\Omega$

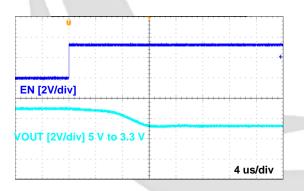

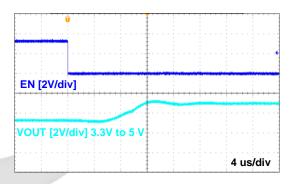

Figure 14. V<sub>OUT</sub> Switchover from 5 V to 3.3 V V<sub>IN1=5</sub> V, V<sub>IN2=3.3</sub> V C<sub>IN=COUT=1.0</sub>  $\mu$ F, R<sub>L=150</sub>  $\Omega$

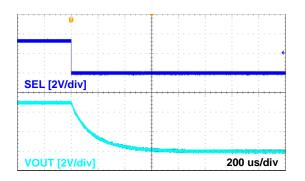

Figure 11. Turn-Off Response VIN1=5 V, CIN=0.1  $\mu F,$  COUT=1.0  $\mu F,$  RL=150  $\Omega$

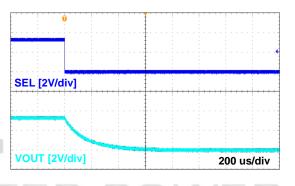

Figure 13. Turn-Off Response V<sub>IN1</sub>=3.3 V, C<sub>IN</sub>=0.1 μF, C<sub>OUT</sub>=1.0 μF, R<sub>L</sub>=150 Ω

Figure 15. V<sub>OUT</sub> Switchover from 3.3 V to 5 V V<sub>IN1</sub>=5 V, V<sub>IN2</sub>=3.3 V C<sub>IN</sub>= C<sub>OUT</sub>=1.0  $\mu$ F, R<sub>L</sub>=150  $\Omega$

| VIN1 [1V/div]<br>VIN2 [1V/div]<br>Iout [50mA/div] |  |

|---------------------------------------------------|--|

|                                                   |  |

|                                                   |  |

| · · · · · · · · · · · · · · · · · · ·             |  |

|                                                   |  |

| VOUT [1V/div]                                     |  |

Figure 16. Reverse Current Blocking When Disabled  $V_{IN1} = V_{IN2} = 0$  V,  $V_{OUT} = 0$  V to 4.5 V,  $C_{IN} = C_{OUT} = 1.0 \ \mu$ F, EN=SEL=0 V

## **APPLICATION INFORMATION**

The GLF4028 is a fully integrated 2 A Power Mux with a fixed slew rate control to limit the inrush current during device turn on. The GLF4028 also has a wide voltage operating range from 2.5 V to 5.5 V. In the off state, the GLF4028 consumes very low leakage current to avoid unwanted power drain from limited input power supplies.

## Input Source Selection

By changing the state of the SEL and EN pins, the GLF4028 offers a manual input selection mode. In each mode, the VOUT connects to one input source.

#### **Input Capacitor**

A capacitor is recommended to be placed close to the V<sub>IN</sub> pin to reduce the voltage drop on the input power rail caused by transient inrush current at start-up. A higher input capacitor value can be used to further attenuate the input voltage drop.

#### **Output Capacitor**

An output capacitor is recommended to minimize voltage undershoot on the output pin during the transition when the switch is turned off. Undershoot can be caused by parasitic inductance from board traces or intentional load inductances. If load inductances do exist, use of an output capacitor can improve output voltage stability and system reliability. The C<sub>OUT</sub> capacitor should be placed close to the VOUT and GND pins.

### **Reverse Current Blocking**

The GLF4028 also prevents the reverse current from the output voltage when both switches are turned off at EN = SEL = 0 V.

#### **Board Layout**

All traces should be as short as possible to minimize parasitic inductance effect. Wide traces for VIN, VOUT, and GND will help reduce signal degradation and parasitic effects during dynamic operations as well as improve the thermal performance at high load current.

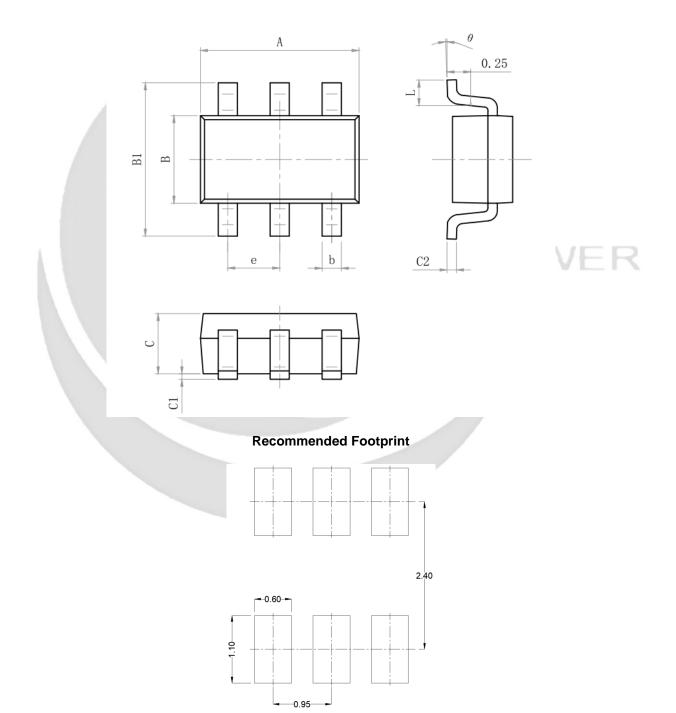

# PACKAGE OUTLINE

| Size<br>Mark | Min(mm) | Max(mm)   | Size<br>Mark | Min(mm) | Max(mm) |

|--------------|---------|-----------|--------------|---------|---------|

| А            | 2.82    | 3.02      | С            | 1.05    | 1.15    |

| е            | 0.9     | 95 (BSC)  | C1           | 0.03    | 0.15    |

| b            | 0.28    | 0.45      | C2           | 0.12    | 0.23    |

| В            | 1.50    | 1.50 1.70 |              | 0.35    | 0.55    |

| B1           | 2.60    | 3.00      | θ            | 0°      | 8°      |

## TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

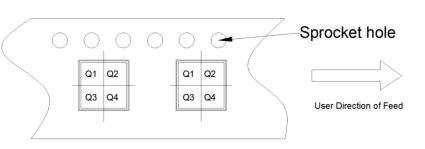

**QUADRANT ASSIGNMENTS PIN 1 ORIENTATION TAPE**

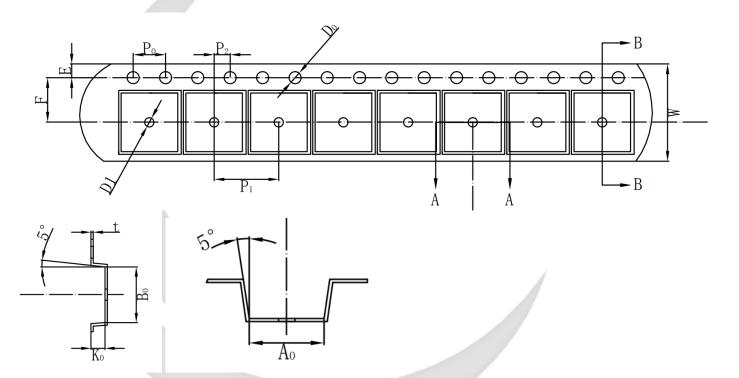

#### TAPE DIMENSIONS

| Device       | Package | Pins | SPQ  | Reel Diameter<br>(mm) | Reel Width<br>W1 | A0   | В0   | К0   | P1 | w | Pin1 |

|--------------|---------|------|------|-----------------------|------------------|------|------|------|----|---|------|

| GLF4028-T2G7 | SOT23-6 | 6    | 3000 | 178                   | 9                | 3.25 | 3.30 | 1.38 | 4  | 8 | Q3   |

Remark:

- A0: Dimension designed to accommodate the component width

- B0: Dimension designed to accommodate the component length

- C0: Dimension designed to accommodate the component thickness

- W: Overall width of the carrier tape

- P1: Pitch between successive cavity centers

## **SPECIFICATION DEFINITIONS**

# GLF4028

## High Efficiency Power Mux IC

| Document<br>Type             | Meaning                                                                                                                                                                                                                                                                                                                                                                                                   | Product Status          |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Target<br>Specification      | This is a target specification intended to support exploration and discussion of critical needs for a proposed or target device. Spec limits including typical, minimum, and maximum values are desired, or target, limits. GLF reserves the right to change limits at any time without warning or notification. A target specification in no way guarantees future production of the device in question. | Design /<br>Development |

| Preliminary<br>Specification | This is a draft version of a product specification. The specification is still<br>under internal review and subject to change. GLF reserves the right to<br>change the specification at any time without warning or notification. A<br>preliminary specification in no way guarantees future production of the<br>device in question.                                                                     | Qualification           |

| Product<br>Specification     | This document represents the anticipated production performance characteristics of the device.                                                                                                                                                                                                                                                                                                            | Production              |

## DISCLAIMERS

Information in this document is believed to be accurate and reliable, however GLF assumes no liability for errors or omissions. Device performance may be impacted by testing methods and application use cases. Users are responsible to independently evaluate the applicability, usability, and suitability of GLF devices in their application. In no case will GLF be liable for incidental, indirect, or consequential damages associated with the use, misuse, or sale of its product. Customers are wholly responsible to assure GLF devices meet their system level and end product requirements. GLF retains the right to change the information provided in this data sheet without notice.